EMC Design Guidelines

These Electromagnetic Compatibility (EMC) design guidelines are here to help you understand the basics of how to make a good EMC PCB design or EMC cabling design. Good in this context means: low Electromagnetic Interference (EMI).

Following these guidelines helped many engineers succeed in the EMC testing of several products. However, be aware that guidelines alone cannot do magical things to your design. Be wary! However, getting the basics right will reduce the pain of EMC testing and increase the chances of right-first-time. And that is all that we want, right?

Table Of Content

Preface to the guidelines:

EMC design guidelines for PCBs and cablings:

-

Guideline #1 – Never route signals over split reference planes!

-

Guideline #2 – Always consider the return current.

-

Guideline #3 – Decoupling: use low-inductance capacitors and planes.

-

Guideline #4 – Use ground planes on PCB for shielding.

-

Guideline #5 – Route high-frequency signals adjacent to a plane.

-

Guideline #6 – Control rise- and fall-time.

-

Guideline #7 – Keep clock lines as short as possible.

-

Guideline #8 – Fill top and bottom layers with circuit GND.

-

Guideline #9 – Add stitching vias around high-speed signal vias.

-

Guideline #10 – Add a capacitor close to every pin of a connector.

-

Guideline #11 – Connect circuit GND to chassis at IO area.

-

Guideline #12 – Lay cables along chassis (GND/earth).

-

Guideline #13 – Don’t use cable shield as signal conductor for low-frequency signals.

-

Guideline #14 – Cable shield grounding on only one end for low-frequency signals.

-

Guideline #15 – Cable shield grounding on both ends for high-frequency signals.

-

Guideline #16 – Minimize loop area of signals in cables .

-

Guideline #17 – Avoid electrical balance changes.

Most Common EMC Issues

The guidelines presented on this website are biased by the author’s own experience, gathered during many years of electronics development, firmware programming, and systems engineering. This should be mentioned here as a kind of disclaimer so that you, the reader, can better understand how to weigh and classify the guidelines presented here.

From the author’s own experience, these are the most common EMC issues during product development:

-

Radiated emissions. Many products regularly fail radiated emissions EMC testing from 30MHz to 6GHz according to CISPR 32 or CISPR 11. Most issues typically occur in the frequency range f<1GHz, where the causes of radiation are usually cables or units within the system that are not grounded properly. If the emission limits for f>1GHz cannot be met, the unintentional radiator can most probably be found on a PCB (clock lines, single-ended high-speed data lines, small PCB-structures).

-

Radiated immunity. Radiated immunity for most products requires testing according to IEC 61000-4-3. Usually, sensors are the most sensitive elements in a product. This is why sensors require special attention during the design and EMC immunity testing. Care must be taken that all signal lines to and from a sensor are filtered with the maximum allowed attenuation. However, every filter causes distortions and time delays (phase shift in the frequency-domain). Therefore, ensure that the distortions and time delays are below the allowed maximum. In addition, low-impedance grounding of any sensitive circuit is of utmost importance and the cabling and PCB-structures should be kept as short and small as possible.

-

Electrostatic discharge. Grounding, grounding, grounding. ESD testing is performed according to IEC 61000-4-2. Every electrically floating part of a product increases the chance of failing the ESD-test because it increases the chance that undesired currents caused by ESD-pulses flow along wires and PCB signal lines and eventually lead to damaged integrated circuits or disturbed signals.

Return Current In GND Planes

We try to avoid the terms ground plane and GND plane in our guidelines. Whenever appropriate, we use the terms signal return plane, return signal reference plane, or simply: reference plane. Why this?

Currents flow in loops. A current does always return to its source. A common issue is that engineers tend to forget about this when they design PCBs and electronics systems, especially when they design digital systems where you can only see the signal traces from chip to chip, and the return current flows through the "GND symbols" in the schematic. The majority of EMC problems (e.g. radiated emission, ESD) involve high-frequency signals (several megahertz - MHz). It is important to understand that a return current of a signal above about 50kHz prefers to flow close to the forward current, e.g. directly under the forward current in an adjusted power supply or ground plane - the so-called return signal reference plane.

The following two impressive images compare the return currents through a reference plane of a low-frequency signal vs. a high-frequency signal (source: EMI Troubleshooting Cookbook for Product Designers). In the left picture, the signal has a frequency of 1kHz, and in the right 1MHz. The difference is obvious and eye-opening! So let's get started with the guidelines and learn more about EMC-compliant design.

EMC Design Guidelines

EMC Guideline # 1 – Never route signals over split reference planes!

Goal = Reduced radiated emission

Do not route signals over split return signal reference planes (GND, power planes)! Never! This leads to unnecessary large current loops (as the current return cannot flow directly underneath the forward current) and large current loops tend to lead to high radiated emission values. The figure below shows the forward current (solid line) and the return current to the source (dashed line).

Rule Of Thumb #1: Whenever in doubt, do not split return current reference planes (GND, power planes), go with a solid filled reference plane instead. There should always be at least one solid reference plane closely adjacent to high-frequency signals (f>1MHz).

EMC Guideline #2 – Always consider the return current.

Goal = Reduced radiated emissions and common-impedance coupling.

Always consider the return current! Always! And with the return current in mind: minimize the common return current paths of high-current circuits (e.g., motors) and sensitive circuits (e.g., unamplified sensor signals) because these common paths lead to common-impedance coupling. In addition, try to minimize the loop area A [m2] between the forward and return current of high-frequency signals because these loops may lead to unintended radiated emissions.

Hint: Assuming a high-frequency signal A (f>1MHz) along a PCB trace on layer 1 and a reference plane (e.g., GND or power plane) on layer 2, the return current of the high-frequency signal A on the reference plane prefers to flow directly under the trace of A because the high-frequency return current always takes the path of the least inductance.

Goal = reduced radiated emissions and common-impedance coupling.

EMC Guideline #3 – Decoupling: use low-inductance capacitors

and planes.

Decoupling is important! Always consider decoupling! For PCBs, we can distinguish between two cases:

-

Local decoupling. For PCBs WITHOUT closely spaced power supply and GND planes, we speak of local decoupling (see the left figure below).

-

Global decoupling. For PCBs WITH closely spaced power supply and GND planes, we speak of global decoupling (see the right figure below).

Hint: Decoupling depends on the number of PCB layers and stackup.

-

Two- and single-layer PCBs. For single or two-layer PCB designs, place the decoupling capacitors as close as possible to every power supply pin of every chip of the PCB. This refers to local decoupling.

-

Multi-layer PCBs. In the case of multi-layer PCB designs with closely spaced GND and power planes (<0.25mm, <10mils), the decoupling capacitor location is not as critical as for single- or two-layer designs because the closely spaced planes act as an efficient decoupling capacitor for high-frequencies (>1MHz) and the actual decoupling capacitor acts as a global decoupling capacitance. However, more important than the location of the decoupling capacitor is that the power supply and GND pins of the integrated circuits are connected with low inductance (multiple vias) to the respective planes.

EMC Guideline #4 – Use ground planes on PCB for shielding.

Goal = Reduced interference on circuit board.

Use solid filled reference planes (e.g., GND or power supply planes) on a PCB to separate noisy signals (e.g., motor signals) from sensitive signals (e.g., unamplified sensor signals). The reference plane will act as a shield and will lower electromagnetic interference (EMI). However, be aware that such a copper shield will primarily be effective for E-fields at any frequency and high-frequency H-fields (f>1MHz), but not for low-frequency H-fields because copper has low relative permeability m0r and does not act as a shield against low-frequency magnetic fields.

EMC Guideline #5 – Route high-frequency signals adjacent to a

plane.

Goal = Reduced radiated emissions.

High-frequency signals are always to be routed close to an adjacent solid reference plane (GND or power supply plane, which acts in this case as a high-frequency ground). For single-layer designs: use guard traces close to the high-frequency signals where the return currents can flow or GND copper fill.

EMC Guideline #6 – Control rise- and fall-time.

Goal = Reduced radiated emissions.

Increase the rise- and fall-time of any digital signal (especially clock signals) as far as possible. A short rise- and fall-time means larger signal bandwidth and, therefore, more high-frequency content in a digital signal, which could lead to radiated emissions or reflections in the case of a long transmission line (compared to the wavelength of the high-frequency content).

Rule of thumb: Add a series resistor (typically 33Ω) close to the driver’s output to reduce the rise- and fall-time.

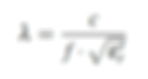

Rule of thumb: The highest significant frequency content fmax [Hz] in a digital signal does not depend on the first harmonic (fundamental frequency). Instead, it depends on the rise- and fall-time:

where, t10%-90% [sec] is the rise- and/or fall-time (whichever is smaller) from 10% to 90% of the slope of a digital signal.

Rule of thumb: Every PCB trace of length longer than λ/10 [m] should be considered a transmission line and no longer as a simple interconnection (where λ [m] is the wavelength). This means that such a trace should be laid out with controlled impedance Z0 [Ω]. In other words: avoid impedance changes or discontinuities along the PCB trace, as these impedance changes or discontinuities could lead to reflections or ringing. Reflections and ringing affect the signal integrity and lead to increased electromagnetic radiation.

EMC Guideline #7 – Keep clock lines as short as possible.

Goal = Reduced radiated emission

To paraphrase the honorable Henry W. Ott: Get paranoid about clock routing! Take care of clock lines and their return current paths and keep them as short as possible!

EMC Guideline #8 – Fill top and bottom layers with circuit GND.

Goal = Reduced radiated emission

Fill the top and bottom layers of a PCB with a solid ground plane around the signals (copper area) and metalize the PCB edges. This helps minimize radiated emission because the filled GND areas at the top and bottom layers shield inner-layer signals and prevent radiation. Moreover, the filled copper areas help maintain a low impedance return current path and short current loops.

Important: Do not forget to place a grid of ground stitching vias throughout the whole PCB (otherwise, some small copper islands will start to radiate and you will get more radiation than without the solid copper fill)! This is very important! The rule of thumb in this section below presents a method of determining the maximum distance between stitching vias.

The figure below shows a profile view of a multi-layer PCB with metalized edges.

In addition, plated PCB outside edges (connected to circuit GND) help prevent the inner PCB layers from radiating. The plated PCB edges also help increase the cooling efficiency of a PCB because there is an additional copper surface where heat exchange can occur. The additional costs for metalized PCB edges are low.

Rule of thumb: When filling top and bottom layers with ground (copper pour), it is best practice to add a grid of ground stitching vias over the whole PCB. Otherwise, some small GND copper areas would tend to radiate! The distance between these vias within that grid depends on the highest frequency fmax [Hz] on the PCB. Given a signal with wavelength λ [m], it is a rule of thumb that a stub or trace of length ≥λ/10 starts to become a problem (regarding radiation) and a trace of length <λ/20 will not be a problem (in between λ/10 and λ/20 is a gray area). Therefore, the distance between the vias should be shorter than l=10 of fmax [Hz]. The wavelength λ [m] of a sinusoidal signal running through a PCB signal trace is according to equation:

where, c is the speed of light (2.998e8 m/sec), f [Hz] is the frequency of a sinusoidal signal and εr' is the effective relative permeability of the materials around the copper trace.

But how to determine fmax [Hz] or λ/10 [m], respectively? Usually, the highest frequency fmax [Hz] on a board can be found in the digital signals, e.g., the clock signals:

where, t10%-90% [sec] is the rise- and/or fall-time (whichever is smaller) from 10% to 90% of the slope of a digital signal.

The table below shows example values of high-frequency digital signals rise/fall-time, their corresponding highest frequency content fmax [Hz] and λ/10-values (as mentioned above: the recommended distance between the vias of the grid of vias is <λ/10).

EMC Guideline #9 – Add stitching vias around high-speed

signal vias.

Goal = Reduced radiated emission

Imagine the following scenario: a high-speed signal changes from one plane to another plane of a PCB. In order to minimize ground bounce, the return current path impedance should be minimized [1]. There are these two options, depending on the return current path:

-

Identical return current reference nets. If the two planes have the same reference net with identical electrical potential (e.g., GND), add two or three stitching vias (between the reference planes) close to high-speed signal via. These stitching vias help keep current loops and, therefore, the inductance as small as possible.

-

Different return current reference reference nets. If the two reference planes are DC isolated, ensure that the two reference planes are coupled with the lowest impedance possible. This can be achieved with the thinnest possible dielectric layer between them (see figure below).

EMC Guideline #10 – Add a capacior to every pin of a connector.

Goal = Reduced radiated emission, conducted immunity

Filtering of signals directly at the connector is very important! This helps increase ESD immunity to a PCB, reduce radiated emissions, and increase immunity to coupled burst signals on IO-cables. Every signal or power supply line that enters or leaves a PCB needs a filter element, e.g., a ceramic capacitor. One side of the capacitor should be connected close to the connector pin, the other pin tied to the ground plane with low inductance. The table below proposes some common capacitor values depending

on the signal’s data rate (see table below).

Hint: Signal lines that leave a device (e.g., a connector that people can touch with their hands) is exposed to ESD (2kV, 4kV, 6kV, 8kV). In this case, use capacitors with a high voltage rating (e.g., >250V, depending on capacitance and ESD test voltage and other components involved, e.g., like ferrite beads between connector pin and capacitor or conductor length).

EMC Guideline #11 – Connect circuit GND to chassis at IO area.

Goal = Reduced radiated emission, conducted immunity

Bound a circuit GND to chassis at the area where a cable leaves/enters the chassis. Connect it with very low impedance! It is important that GND and chassis have the same potential in the IO area:

-

It prevents unintended radiation, as the GND shows a minimum voltage difference

to the chassis (earth). -

It makes the IO-signal filters on a PCB most effective and keeps ESD pulses away

from the circuits on the board. Why? Because incoming noise and interference from the cable or connector can directly flow back to the source along chassis and earth.

EMC Guideline #12 – Lay cables along chassis (GND, earth).

Goal = Reduced radiated emission

Whenever possible, lay cables constantly along the chassis. This keeps the electromagnetic field generated by the voltages and currents in the cable at a minimum radiation level. The word constantly is essential because when laying out cables constantly along a chassis, there is no change in electrical balance (a change in electrical balance leads to common-mode currents).

EMC Guideline #14 – Cable shield grounding on only one end for low-frequency signals.

EMC Guideline #13 – Don’t use cable shield as signal conductor for low-frequency signals.

Goal = Increased immunity

The cable shield should not be one of the signal conductors for low-frequency signals because of the potential interference with the ground loop current in the shield.

Hint: This rule does not apply for high-frequency signals, where the signal return current and the noise current are separated by the skin effect within the shield (return current of the high-frequency signal flows on the surface of the inner side of the shield and the noise current on the outer surface).

Goal = Increased immunity to electric-fields

It may lead to problems when laying both ends of a cable shield to ground for low-frequency signals because ground loop currents in the shield could interfere with the signals inside the cable.

Rule of thumb: For shielding of low-frequency (<100kHz) signals:

-

Shielding against E-fields: Lay only one end of the shield to ground (with low impedance) to avoid noise current through the shield (e.g., induced by magnetic fields or ground loop currents).

-

Shielding against H-fields: Lying only one end of the shield to ground does not protect from H-field interference. If protection against low-frequency H-fields is needed, a shield with relative permeability µ0r>>1 is necessary. Twisting does also help to protect against H-field coupling.

If you are in control of only one side of the cable shield (because at the other end of the cable is an unknown device from various manufacturers), then lay the cable shield to ground with low inductance (no pigtails, use a 360° shield clamp) or implement a hybrid ground. A hybrid ground is a compromise for shielding against high-frequency signals, while minimizing low-frequency ground loop currents in the shield (see figure below): Lay the cable shield to ground with a resistor (to reduce the ground loop current in the shield for low-frequency signals) and add a parallel capacitor to that resistor (to allow high-frequency signals to flow through the cable shield).

EMC Guideline #15 – Cable shield grounding on both ends for high-frequency signals.

Goal = Increased immunity, reduced magnetic-field emissions

It is a must to lay both ends of high-frequency signal cable shields to ground with low inductance (no pigtails, use a 360° shield clamp or the like). Rule of thumb: For high-frequency (>1MHz) signals:

-

The shield can be used as signal return path for high-frequency signals, because the outside noise source.The induced noise current in the shield helps to cancel out the magnetic field of the signal return current and the noise current are separated by the skin effect.

-

To reduce the magnetic field emissions from a signal in a shielded cable, the shield has to be laid on ground on both ends

EMC Guideline #16 – Minimize loop area of signals in cables.

Goal = Increased immunity to magnetic-fields.

The best way to protect a signal from magnetic fields is to reduce the current loop area A [m^2]. Minimizing the loop area A [m^2] in case of a cable means twisting the wires of the forward and return current or using neighbor conductors for the forward and return current in flat ribbon cables.

EMC Guideline #17 – Avoid electrical balance changes.

Goal = Reduced radiated emissions

A change from electrically balanced to unbalanced and vice versa (mode conversion) is called an electrical balance change (balanced and unbalanced transmission lines are topic in section 7.9). Electrical balance changes lead to common-mode currents. And we do not want common-mode currents! Common-mode currents are often the cause for unintended radiated emissions. Thus, mode conversions should be avoided. The maximum common-mode voltage VCM;max [V] generated due to mode change is VCM;max = ΔhmaxVDM = 0.5VDM, where h is the imbalance factor and ΔhmaxVDM is the maximum imbalance factor change.

Avoiding electrical balance changes for cables connected to a PCB means:

-

If the signal is balanced, stay balanced (twisted pair, flat cable, see figure below).

-

If the signal is unbalanced, stay unbalanced (coaxial, multi-layer flat cable, see figure below).

Avoiding electrical balance changes for filters means:

• If a signal is balanced, add the identical filters to both signal lines. See figure below.

• If a signal is unbalanced, add only filters to the signal line. See figure below.